[서울=뉴스핌] 정승원 기자 = SK하이닉스는 혁신 기술 역량과 D램 기술 로드맵에 대해 조명하는 좌담회를 진행했다고 10일 밝혔다.

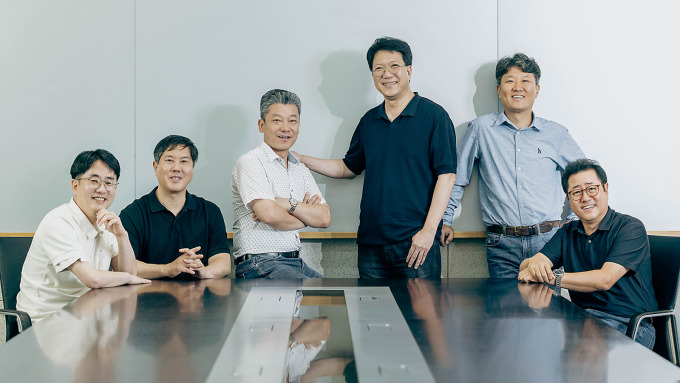

이 자리에는 1c 기술 개발을 주도한 오태경 SK하이닉스 부사장(1c Tech TF), 조주환 부사장(DRAM 설계), 조영만 부사장(DRAM PI), 정창교 부사장(DRAM PE), 손수용 부사장(개발 TEST), 김형수 부사장(DRAM AE)이 참석했다.

앞서 SK하이닉스는 극도로 미세화된 D램 공정 기술의 한계를 돌파하며 새로운 이정표를 세운 바 있다. SK하이닉스는 지난달 29일 세계 최초로 10나노급 6세대(1c) 미세공정을 적용한 16Gb(기가비트) DDR5 D램을 개발하는 데 성공했다고 밝혔다.

1c 기술은 10나노대 초반의 극미세화된 메모리 공정 기술이다. 1c 기술을 적용한 DDR5의 동작 속도는 8Gbps(초당 8기가비트)로 이전 세대인 1b DDR5보다 11% 빨라졌으며 전력 효율은 9% 이상 개선됐다.

SK하이닉스는 EUV 공정에 신소재를 개발해 적용하는 한편 설계 기술 혁신을 통해 공정 효율을 극대화했으며 원가 절감도 이뤄냈다.

오태경 부사장은"1c 기술 개발을 총괄한 1c 테크 TF의 가장 큰 목표는 1등 개발이었다"며 "우리는 이미 우수성이 증명된 1b 플랫폼을 확장하는 방식으로 개발하는 전략을 선택했다. 기존의 '테스트-설계-양산 준비'의 3단계 개발 방식을 '설계-양산 준비' 2단계로 효율화했고 커패시터(Capacitor) 모듈과 같은 고난도의 기술 요소를 양산 공정에서 바로 개발하는 방식을 택해 전세대 제품 대비 2개월이나 단축 기술 개발에 성공할 수 있었다"고 말했다.

조주환 부사장은 "최고 경쟁력이 입증된 1b 기술을 경험한 덕분에 기술적 위험도는 줄었으나 작아진 셀 크기와 커진 저항으로 인해 여전히 해결해야 하는 문제들이 많았다"며 "회로 밀도와 센싱 성능을 높이는 등 다양한 설계 혁신을 통해 데이터 처리 속도는 높이고 전력 소비는 줄이는 데 성공했다"고 강조했다.

조영만 부사장은 "1b 플랫폼을 확장하는 방식은 1c 기술의 공정 고도화 과정에서 시행착오를 줄이는 데 주효했다"며 "1b의 경험을 바탕으로 1c 기술에서 발생할 수 있는 문제를 사전에 예측하고 해결할 수 있었다. 특히, 트랜지스터 열화와 신규 소재 적용에 따른 품질 리스크를 조기에 발견하고 개선해 미세화된 소자의 신뢰성을 확보할 수 있었다"고 설명했다.

정창교 부사장은 "새로운 기술을 개발할 때 전에 없던 새로운 문제에 직면하게 마련"이라며 "공정이 미세화되면서 과거와는 다른 특성들이 더 중요해지고 이로 인해 수율 저하 등 문제가 발생할 수 있는데 1c 기술에서 주요 성능의 수준을 높이는 트리밍 기술을 활용해 수율과 품질을 확보했다"고 전했다.

SK하이닉스가 D램 시장에서 독보적인 기술 리더십을 발휘할 수 있는 저력으로는 좌담회 참가자 모두 '유기적인 협업'과 '원팀(One Team)' 정신을 꼽았다.

오 부사장은 "TF 운영을 비롯한 일하는 방식의 변화부터 플랫폼 기반 개발, 조기 양산 팹 운영 전략 등 다방면에 혁신이 더해지며 SK하이닉스의 기술 개발 역량은 점점 더 강해지고 있다"며 "무엇보다 구성원들의 원팀 정신이 모든 성과를 견인했다"고 밝혔다.

정 부사장도 "1c 기술 개발 과정에서 가장 중요한 요소는 원팀 문화였다. '최초'라는 타이틀에 따라오는 많은 기술적 도전을 극복하기 위해 각 조직이 긴밀하게 협력하여 문제를 조기 발견했고 해결했기 때문"이라며 "DRAM PE 조직이 스크린 최적화를 진행하는 과정에서 설계 및 공정 조직과의 긴밀한 협업이 핵심적인 역할을 했다"고 강조했다.

SK하이닉스는 연내 1c DDR5의 양산 준비를 마치고 내년부터 시장에 제품을 본격 공급할 계획이다.

origin@newspim.com