미국 제재하에 중국 정부 2.5D/3D 패키징 기술 강조

미국이 SMIC(중신국제)와 화웨이에 대한 반도체 기술 및 제품 수출을 제한하는 규제를 연이어 발표한 이후 중국정부는 미국 반도체 제재에 대한 대책을 여러 차례 논의했다.

그 중에 대표적인 회의 중 하나가 2021년 5월 국무원 부총리 류허(刘鹤) 주재로 열린 중국 '국가과학기술 영도소조 (国家科技体制改革和创新体系建设领导小组)' 회의 끝부분에 개최된 '포스트 무어의 법칙 시대를 맞이한 반도체산업의 잠재 파괴적 기술에 대한 전문가 토론'이다.

이때 많은 매체들은 회의 결과를 소개하면서 중국이 미국과의 반도체 기술전쟁에서 부족한 반도체 기술을 만회하고자 첨단 패키징 기술을 발전시킬 것을 강조했다고 전했다. 특히 포스트 무어 시대의 파괴적 기술로 첫째 집적 회로 칩의 기능을 확장하기 위해 트랜지스터 크기의 지속적인 감소에 의존하지 않는 특수 공정 개발에 역점을 두기로 했다. 또 다양한 기능을 갖춘 칩과 구성 요소를 함께 조립하여 이기종을 통합하는 방안 등 2가지 기술 개발을 선정했다고 보도했다.

글싣는 순서

1. 중국 반도체 굴기, 한국 따라잡나

2. 중국 반도체 설계 기술 현주소

3. 中 파운드리 점유율 확대와 한계

4. 후공정 세계 2위 中 2.5D/3D 패키징 육성 전력

5. 반도체 굴기 '보틀넥' 장비산업 공급망 회복은?

6. 무서운 잠재력 중국 반도체 소재

7. 이미지 센서 반도체 세계 3위

8. 세계를 리드하는 중국 AI반도체

9. 반도체 굴기 지탱하는 자동차 반도체 위용

10. 중국 휴대폰 반도체 놀라운 시장 규모

11. 다양한 응용 中 MCU 반도체 시장

12. 3세대 반도체 세계 1등의 꿈

13. 반도체 협력 한중 상생 방안

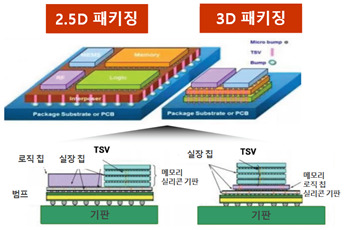

여기서 '이기종 통합'은 서로 다른 기능을 가진 다이(Die, 가공된 웨이퍼 상에서 잘라낸 IC 원판 하나)를 플립 칩 본딩(Flip Chip Bonding)하여 집적도를 높이는 2.5D 패키징 기술을 말하는 것이다.

예를들어 인공지능 GPU를 만들기 위해서는 CPU 모듈과 메모리 모듈을 하나의 칩에 넣어야 하는데, 완전히 다른 칩을 새로 설계하는 것이 기존의 방법이었다면, 이것을 패키징 단계에서 하나의 패키징 베이스 위에 CPU 다이와 메모리 다이를 배치하고, 플립 칩 본딩 기술로 연결하여 하나의 칩으로 패키징하는 기술이다.

또한 '트랜지스터 크기 감소에 의존하지 않는 공정'은 동종의 다이를 스택으로 쌓아올리고 실리콘 관통 전극(Through Silicon Via, TSV)이라고는 실리콘 기둥을 세워 다이를 3차원적으로 서로를 연결시켜 집적도를 높이는 3D 패키징 기술을 말한다. 현재 삼성전자, SK하이닉스가 이 기술을 적용하여 HBM(High Bandwidth Memory)을 양산하고 있다.

2.5D/3D SiP(System in Package) 패키징 기술은 낮은 기술과 가격으로 반도체의 집적도를 높이고 성능을 혁신적으로 향상시키는 방법이지만 높은 전력 소비가 해결해야할 숙제로 남아있다.

14나노로 7나노 효과? 화웨이 3D 패키징 기술 난제

페키징 기술 관련하여, 2022년 중반 현시점에서 중국의 반도체 관련 인터넷 사이트에서 토론되는 재미있는 '핫이슈'가 하나 있다.

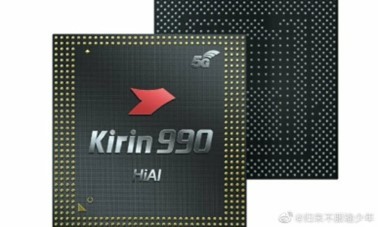

화웨이가 2019년 자체 기술로 개발한 5G SoC(스마트폰 프로세서) '기린'(KIRIN)990 칩은, 미국의 수출 제재를 받은 후, 2020년 9월 대만 TSMC가 파운드리 서비스 중단을 서비스 하면서 더 이상 생산이 되지 않고 있다.

이 칩은 당시 최첨단 기술인 7나노 공정으로 개발되었고 중국 내에는 7나노 생산 설비가 없어서 생산을 할 수가 없기 때문에 화웨이가 대안으로 중국 내에 존재하는 14나노 생산설비를 이용해서 7나노 성능을 내는 칩을 만들어 내면 되지 않느냐는 논쟁이다.

화웨이는 3D 패키징 기술을 활용하여 14나노 칩 두 개를 쌓아 올리면 7나노 칩 성능을 낼 수 있을 것으로 기대된다고 주장하는 이들이 많다.

하지만, 이 논쟁에서는 칩의 적층(Stacking)은 전력 소모, 공간, 방열 등 세 가지 문제를 부수적으로 야기한다는 사실을 놓치고 있다.

우선, 전력 소모부터 보면 휴대전화 등 전자제품 중 디스플레이 화면 이외에 전기를 많이 소비하는 것이 SoC 이다. 그래서 선폭을 줄여 전기 소모를 감소시키고 있다. Apple M2칩은 5나노 기술을 적용했고, 퀄컴 Snapdragon 8 Gen1은 4나노 기술을 적용했다. 가뜩이나 14나노미터짜리 칩 하나도 버거운데 두 개를 겹쳐 놓으면 전력 소모를 감당할수 없을 것이다.

둘째, 반도체 소비 전력 증가는 발열 증가를 의미한다. 스마트폰은 배터리·모터·카메라 모듈 등을 내장한 뒤 열을 발산할 수 있는 공간이 많지 않을 정도로 내부 공간이 한정돼 있어 발열을 막을 방법이 없다.

세째, 칩이 쌓이면 두께가 두꺼워진다. 단층짜리 칩의 두께만 해도 스마트폰에서는 두꺼운데 2개를 겹쳐 놓으면 더욱 두꺼워진다. 이 칩이 휴대전화에 들어가는 것은 현실적이지 않다.

이상과 같이 화웨이가 현재 중국 실정상 7나노 생산시설이 없어 자체 5G 칩을 생산하지 못하는 난국을 타개하기 위해 디각적인 노력을 기울이고 있는 것으로 보이는데, 실제 효과적인 대안이 나오기는 그리 쉽지 않아 보인다.

세계 M/S 2위, 중국 반도체 후공정 분야에서 약진세

반도체의 세계적 분업체계에 있어 중국은 반도체 후공정 분야에서 대만에 이어 세계 2위의 시장점유율을 차지하고 있다. 상대적으로 경쟁력이 있는 분야이다.

향후 중국 후공정 산업은 관련 기업의 수량도 풍부하고 기업간의 경쟁도 매우 치열해서 자생적인 발전이 이루어 질 것으로 보인다. 또한 중국정부의 국가 반도체펀드가 업계 개발 기업들의 국내 경쟁력 강화 및 관련 기업들의 세계화에 많은 지원을 하고 있는 것도 분명하다.

<필자 약력>

베이징대학 한반도연구소 연구원

중국 한국창업원 원장

SV인베스트먼트 고문

전 산업은행 베이징지점 고문

서울대 조선해양공학 학사/석사

베이징= 최헌규 특파원 chk@newspim.com